## TMS320C674x/OMAP-L1x Processor External Memory Interface B (EMIFB)

# **User's Guide**

Literature Number: SPRUFL7A April 2009

### Contents

| Prefa | се     |                                                           | 6   |

|-------|--------|-----------------------------------------------------------|-----|

| 1     | Introd | uction                                                    | . 8 |

|       | 1.1    | Purpose of the Peripheral                                 | . 8 |

|       | 1.2    | Features                                                  | . 8 |

|       | 1.3    | Functional Block Diagram                                  | . 8 |

| 2     | Archit | ecture                                                    | . 9 |

|       | 2.1    | Clock Control                                             | . 9 |

|       | 2.2    | EMIF Requests                                             | . 9 |

|       | 2.3    | Pin Descriptions                                          | . 9 |

|       | 2.4    | Pin Multiplexing                                          | 10  |

|       | 2.5    | Memory Map                                                | 10  |

|       | 2.6    | SDRAM Controller and Interface                            | 10  |

|       | 2.7    | Reset and Initialization Considerations                   | 28  |

|       | 2.8    | Interrupt Support                                         | 28  |

|       | 2.9    | EDMA Event Support                                        | 28  |

|       | 2.10   | Power Management                                          |     |

|       | 2.11   | Emulation Considerations                                  | 31  |

| 3     | Regist | ers                                                       | 32  |

|       | 3.1    | Revision ID Register (REVID)                              | 32  |

|       | 3.2    | SDRAM Configuration Register (SDCFG)                      | 33  |

|       | 3.3    | SDRAM Refresh Control Register (SDRFC)                    | 35  |

|       | 3.4    | SDRAM Timing 1 Register (SDTIM1)                          | 36  |

|       | 3.5    | SDRAM Timing 2 Register (SDTIM2)                          | 37  |

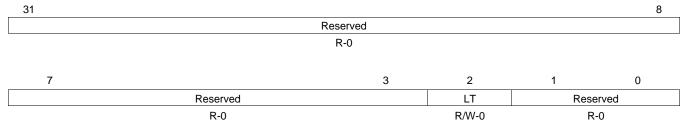

|       | 3.6    | SDRAM Configuration 2 Register (SDCFG2)                   | 38  |

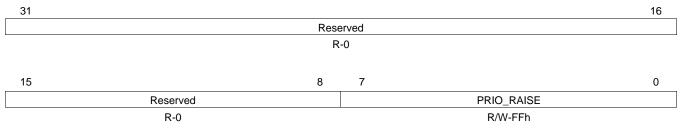

|       | 3.7    | Peripheral Bus Burst Priority Register (BPRIO)            |     |

|       | 3.8    | Performance Counter 1 Register (PC1)                      | 40  |

|       | 3.9    | Performance Counter 2 Register (PC2)                      |     |

|       | 3.10   | Performance Counter Configuration Register (PCC)          |     |

|       | 3.11   | Performance Counter Master Region Select Register (PCMRS) |     |

|       | 3.12   | Performance Counter Time Register (PCT)                   |     |

|       | 3.13   | Interrupt Raw Register (IRR)                              |     |

|       | 3.14   | Interrupt Mask Register (IMR)                             |     |

|       | 3.15   | Interrupt Mask Set Register (IMSR)                        |     |

|       | 3.16   | Interrupt Mask Clear Register (IMCR)                      |     |

| Appe  | ndix A | Example Configuration                                     |     |

|       | A.1    | Hardware Configuration                                    |     |

|       | A.2    | Software Configuration                                    |     |

| Appe  | ndix B | Revision History                                          | 52  |

### List of Figures

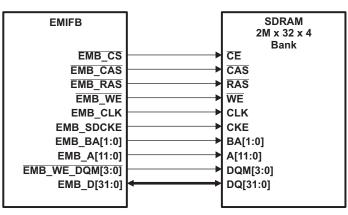

| 1   | EMIFB Functional Block Diagram                               | . 8 |

|-----|--------------------------------------------------------------|-----|

| 2   | Timing Waveform of SDRAM PRE Command                         | 11  |

| 3   | EMIFB to $2M \times 16 \times 4$ bank SDRAM Interface        | 12  |

| 4   | EMIFB to $2M \times 32 \times 4$ bank SDRAM Interface        | 12  |

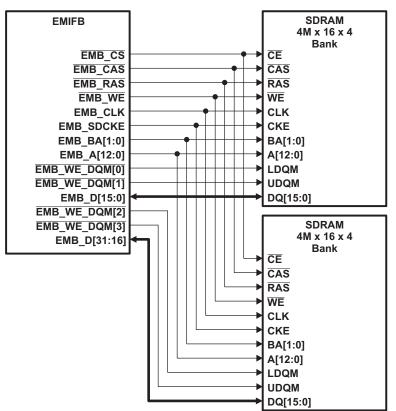

| 5   | EMIFB to Dual 4M $\times$ 16 $\times$ 4 bank SDRAM Interface | 13  |

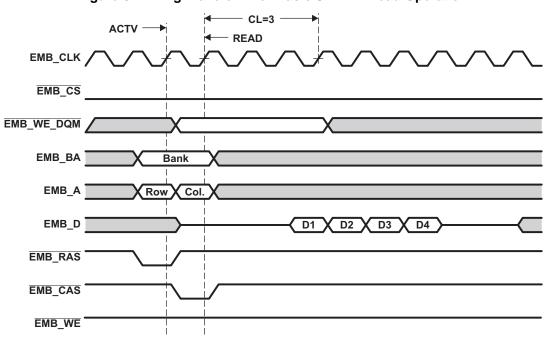

| 6   | Timing Waveform for Basic SDRAM Read Operation               | 21  |

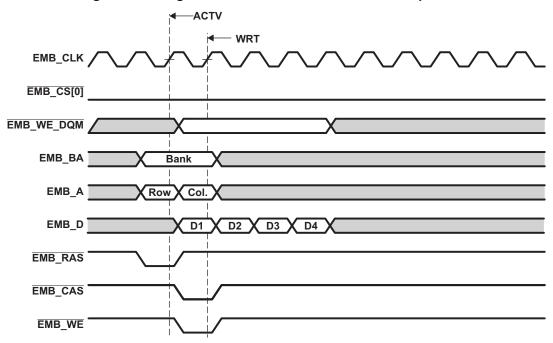

| 7   | Timing Waveform for Basic SDRAM Write Operation              | 22  |

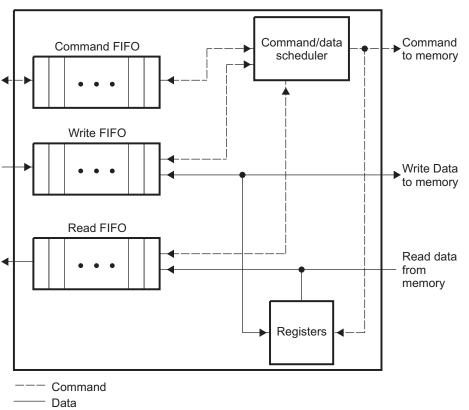

| 8   | EMIFB Memory Controller FIFO Block Diagram                   | 25  |

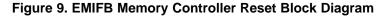

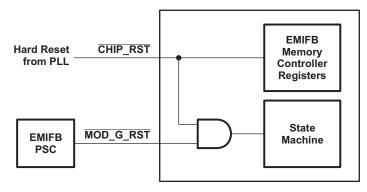

| 9   | EMIFB Memory Controller Reset Block Diagram                  | 28  |

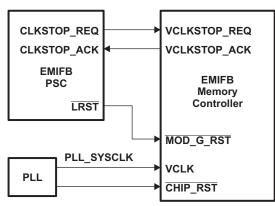

| 10  | EMIFB Memory Controller Power and Sleep Controller Diagram   | 29  |

| 11  | Revision ID Register (REVID)                                 | 32  |

| 12  | SDRAM Configuration Register (SDCFG)                         | 33  |

| 13  | SDRAM Refresh Control Register (SDRFC)                       | 35  |

| 14  | SDRAM Timing 1 Register (SDTIM1)                             | 36  |

| 15  | SDRAM Timing 2 Register (SDTIM2)                             | 37  |

| 16  | SDRAM Configuration 2 Register (SDCFG2)                      |     |

| 17  | Peripheral Bus Burst Priority Register (BPRIO)               | 39  |

| 18  | Performance Counter 1 Register (PC1)                         | 40  |

| 19  | Performance Counter 2 Register (PC2)                         |     |

| 20  | Performance Counter Configuration Register (PCC)             | 41  |

| 21  | Performance Counter Master Region Select Register (PCMRS)    | 43  |

| 22  | Performance Counter Time Register (PCT)                      | 44  |

| 23  | Interrupt Raw Register (IRR)                                 | 44  |

| 24  | Interrupt Mask Register (IMR)                                | 45  |

| 25  | Interrupt Mask Set Register (IMSR)                           |     |

| 26  | Interrupt Mask Clear Register (IMCR)                         | 47  |

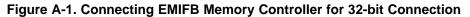

| A-1 | Connecting EMIFB Memory Controller for 32-bit Connection     | 48  |

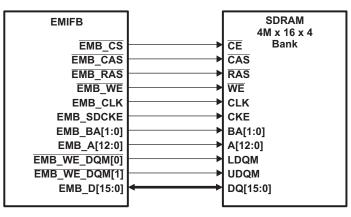

| A-2 | Connecting EMIFB Memory Controller for 16-bit Connection     | 49  |

### List of Tables

| 1   | EMIF Pins Used to Access SDRAM                                               | . 9 |

|-----|------------------------------------------------------------------------------|-----|

| 2   | EMIF SDRAM Commands                                                          | 10  |

| 3   | Truth Table for SDRAM Commands                                               | 11  |

| 4   | Example of 32-bit EMIFB Address Pin Connections                              | 13  |

| 5   | Example of 16-bit EMIFB Address Pin Connections                              | 14  |

| 6   | Description of the SDRAM Configuration Register (SDCFG)                      | 14  |

| 7   | Description of the SDRAM Refresh Control Register (SDRFC)                    | 15  |

| 8   | Description of the SDRAM Timing 1 Register (SDTIM1)                          | 15  |

| 9   | Description of the SDRAM Timing 2 Register (SDTIM2)                          |     |

| 10  | Description of the SDRAM Configuration 2 Register (SDCFG2)                   | 15  |

| 11  | mobile SDRAM LOAD MODE REGISTER Command                                      | 16  |

| 12  | SDRAM/mobile SDRAM LOAD MODE REGISTER Command                                |     |

| 13  | Refresh Urgency Levels                                                       | 18  |

| 14  | PASR Bitfield in SDRAM Configuration 2 Register (SDCFG2) Configuration       |     |

| 15  | Example Mapping from Logical Address to EMIFB Pins for 32-bit SDRAM          | 23  |

| 16  | Example Mapping from Logical Address to EMIFB Pins for 16-bit SDRAM          |     |

| 17  | Example Mapping from Logical Address to EMIFB Pins for mobile SDRAM          |     |

| 18  | SDRAM Memory Controller FIFO Description                                     |     |

| 19  | Reset Sources                                                                |     |

| 20  | EMIFB Base Controller Registers                                              |     |

| 21  | Revision ID Register (REVID) Field Descriptions                              |     |

| 22  | SDRAM Configuration Register (SDCFG) Field Descriptions                      |     |

| 23  | SDRAM Refresh Control Register (SDRFC) Field Descriptions                    | 35  |

| 24  | SDRAM Timing 1 Register (SDTIM1) Field Descriptions                          |     |

| 25  | SDRAM Timing 2 Register (SDTIM2) Field Descriptions                          |     |

| 26  | SDRAM Configuration 2 Register (SDCFG2) Field Description                    |     |

| 27  | Peripheral Bus Burst Priority Register (BPRIO) Field Descriptions            |     |

| 28  | Performance Counter 1 Register (PC1) Field Descriptions                      |     |

| 29  | Performance Counter 2 Register (PC2) Field Descriptions                      |     |

| 30  | Performance Counter Configuration Register (PCC) Field Descriptions          |     |

| 31  | Performance Counter Filter Configuration                                     |     |

| 32  | Performance Counter Master Region Select Register (PCMRS) Field Descriptions |     |

| 33  | Performance Counter Time Register (PCT) Field Description                    |     |

| 34  | Interrupt Raw Register (IRR) Field Descriptions                              |     |

| 35  | Interrupt Mask Register (IMR) Field Descriptions                             |     |

| 36  | Interrupt Mask Set Register (IMSR) Field Descriptions                        |     |

| 37  | Interrupt Mask Clear Register (IMCR) Field Descriptions                      |     |

| A-1 | SDCFG Configuration                                                          |     |

| A-2 | SDRFC Configuration                                                          |     |

| A-3 | SDTIM1 Configuration                                                         |     |

| A-4 | SDTIM2 Configuration                                                         |     |

| B-1 | Document Revision History                                                    | 52  |

Preface SPRUFL7A-April 2009

### About This Manual

This document describes the operation of the external memory interface B (EMIFB).

### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

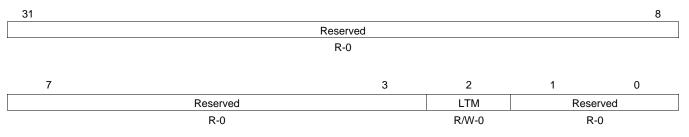

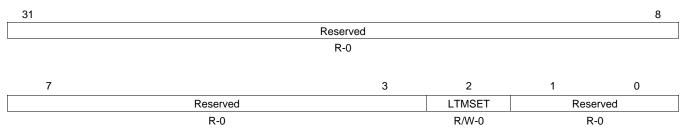

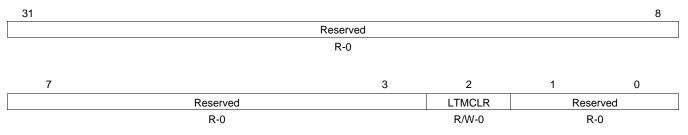

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

### **Related Documentation From Texas Instruments**

The following documents describe the TMS320C674x Digital Signal Processors (DSPs) and OMAP-L1x Applications Processors. Copies of these documents are available on the Internet at <u>www.ti.com</u>. *Tip:* Enter the literature number in the search box provided at www.ti.com.

The current documentation that describes the DSP, related peripherals, and other technical collateral, is available in the C6000 DSP product folder at: <a href="http://www.ti.com/c6000">www.ti.com/c6000</a>.

<u>SPRUGJ0</u> — *TMS320C6743 DSP System Reference Guide.* Describes the System-on-Chip (SoC) including the C6743 DSP subsystem, system memory, device clocking, phase-locked loop controller (PLLC), power and sleep controller (PSC), power management, and system configuration module.

- <u>SPRUFK4</u> TMS320C6745/C6747 DSP System Reference Guide. Describes the System-on-Chip (SoC) including the C6745/C6747 DSP subsystem, system memory, device clocking, phase-locked loop controller (PLLC), power and sleep controller (PSC), power management, and system configuration module.

- SPRUG84 OMAP-L137 Applications Processor System Reference Guide. Describes the System-on-Chip (SoC) including the ARM subsystem, DSP subsystem, system memory, device clocking, phase-locked loop controller (PLLC), power and sleep controller (PSC), power management, ARM interrupt controller (AINTC), and system configuration module.

- <u>SPRUFK9</u> *TMS320C674x/OMAP-L1x Processor Peripherals Overview Reference Guide.* Provides an overview and briefly describes the peripherals available on the TMS320C674x Digital Signal Processors (DSPs) and OMAP-L1x Applications Processors.

- SPRUFK5 TMS320C674x DSP Megamodule Reference Guide. Describes the TMS320C674x digital signal processor (DSP) megamodule. Included is a discussion on the internal direct memory access (IDMA) controller, the interrupt controller, the power-down controller, memory protection, bandwidth management, and the memory and cache.

- SPRUFE8 TMS320C674x DSP CPU and Instruction Set Reference Guide. Describes the CPU architecture, pipeline, instruction set, and interrupts for the TMS320C674x digital signal processors (DSPs). The C674x DSP is an enhancement of the C64x+ and C67x+ DSPs with added functionality and an expanded instruction set.

SPRUG82 — TMS320C674x DSP Cache User's Guide. Explains the fundamentals of memory caches and describes how the two-level cache-based internal memory architecture in the TMS320C674x digital signal processor (DSP) can be efficiently used in DSP applications. Shows how to maintain coherence with external memory, how to use DMA to reduce memory latencies, and how to optimize your code to improve cache efficiency. The internal memory architecture in the C674x DSP is organized in a two-level hierarchy consisting of a dedicated program cache (L1P) and a dedicated data cache (L1D) on the first level. Accesses by the CPU to the these first level caches can complete without CPU pipeline stalls. If the data requested by the CPU is not contained in cache, it is fetched from the next lower memory level, L2 or external memory.

### External Memory Interface B (EMIFB)

### 1 Introduction

This section provides information about the purpose, and use of the external memory interface B (EMIFB). It also provides a block diagram of the EMIFB that shows its internal connections and external pins.

### 1.1 Purpose of the Peripheral

EMIFB memory controller is complaint with the JESD21-C SDR SDRAM memories utilizing either 32-bit or 16-bit of the EMIFB memory controller data bus. The purpose of this EMIFB is to provide a means for the CPU to connect to a variety of external devices including:

• Single data rate (SDR) SDRAM/ mobile SDR SDRAM

### 1.2 Features

For details on features of EMIFB, see your device-specific data manual.

### 1.3 Functional Block Diagram

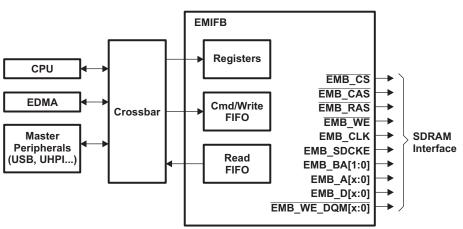

Figure 1 illustrates a high-level view of the EMIFB and its connections within the device. Multiple requesters have access to EMIFB through a switched central resource(indicated as crossbar in the figure). The EMIFB implements a split transaction internal bus, allowing concurrence between reads and writes from the various requesters. Section 2.2 contains further description of the entities internal to the device that can send requests to the EMIFB. Section 2.3 describes the EMIFB external pins and summarizes their purpose when interfacing with SDRAM.

Figure 1. EMIFB Functional Block Diagram

### 2 Architecture

This section provides details about the architecture and operation of the EMIFB SDRAM interface.

### 2.1 Clock Control

For details on EMIFB clock control, see your device-specific System Reference Guide.

### 2.2 EMIF Requests

Depending on the specific device, different sources (CPU, EDMA, and other master peripherals) within the device can make requests to EMIFB. Some of these sources have multiple master ports to the crossbar (EDMA TPTCs) and some share ports to the crossbar (USB). The requests from these sources consist of accesses to SDRAM memory and EMIFB registers. The EMIFB implements internal data FIFOs and a split transaction internal bus to allow concurrence of read and write operations from multiple masters, in an attempt to fully utilize available throughput of the attached memories.

A high-performance crossbar switch exists within the device to provide prioritized requests from the different requesters to the EMIFB. If a request is submitted from two or more sources simultaneously, the crossbar switch will forward the highest priority request to the EMIFB first. Upon completion of a request, the crossbar switch again evaluates the pending requests and forwards the highest priority pending request to the EMIFB.

When forwarding read and write commands to the EMIFB, the crossbar uses a priority arbitration scheme. When the EMIFB receives a request, it may or may not be immediately processed due to prioritization of pending refresh cycles. In some cases, the EMIFB will perform one or more auto refresh cycles before processing the request. For details on the EMIFB's internal arbitration between performing requests and performing auto refresh cycles, see Section 2.6.6. For further details regarding master prioritization within the EMIFB command FIFO, see Section 2.6.13.

### 2.3 Pin Descriptions

Table 1 describes the function of each EMIFB pin.

| Pins(s)         | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EMB_D[x:0]      | I/O | <b>EMIFB data bus.</b><br>The number of available data bus pins varies among devices. See your device-specific data manual for details.                                                                                                                                                                                                                                                                                 |

| EMB_A[x:0]      | 0   | <b>EMIFB address bus.</b><br>When interfacing to an SDRAM device, these pins are primarily used to provide the row and column address to the SDRAM. The number of available address pins depends upon pin multiplexing configuration. See your device-specific data manual for details. The mapping from the internal program address to the external values placed on these pins can be found in Table 15 and Table 16 |

| EMB_BA[1:0]     | 0   | <b>EMIFB bank address.</b><br>When interfacing to an SDRAM device, these pins are used to provide the bank address inputs to the SDRAM. The mapping from the internal program address to the external values placed on these pins can be found in Table 15 and Table 16.                                                                                                                                                |

| EMB_WE_DQM[x:0] | 0   | <b>Byte enables.</b><br>When interfacing to SDRAM, these pins are connected to the DQM pins of the SDRAM to individually enable/disable each of the bytes in a data access.                                                                                                                                                                                                                                             |

| EMB_WE          | 0   | Active-low write enable.<br>When interfacing to SDRAM, this pin is connected to the $\overline{\text{WE}}$ pin of the SDRAM and is used to send commands to the device.                                                                                                                                                                                                                                                 |

| EMB_CS          | 0   | Active-low chip enable pin for SDRAM devices.<br>This pin is connected to the chip-select pin of the attached SDRAM device and is used for<br>enabling/disabling commands. By default, the EMIF keeps SDRAM chip select active, even if the<br>EMIF interface is currently idle.                                                                                                                                        |

#### Table 1. EMIF Pins Used to Access SDRAM

| Pins(s)   | I/O | Description                                                                                                                                                                                                                 |

|-----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EMB_RAS   | 0   | Active-low row address strobe pin.<br>This pin is connected to the RAS pin of the attached SDRAM device and is used for sending<br>commands to the device.                                                                  |

| EMB_CAS   | 0   | Active-low column address strobe pin.<br>This pin is connected to the CAS pin of the attached SDRAM device and is used for sending commands to the device.                                                                  |

| EMB_SDCKE | 0   | <b>Clock enable pin.</b><br>This pin is connected to the CKE pin of the attached SDRAM device and is used for issuing the SELF REFRESH command which places the device in self-refresh mode. See Section 2.6.7 for details. |

| EMB_CLK   | 0   | <b>SDRAM clock pin.</b><br>This pin is connected to the CLK pin of the attached SDRAM device. See Section 2.1 for details<br>on the clock signal.                                                                           |

### Table 1. EMIF Pins Used to Access SDRAM (continued)

### 2.4 Pin Multiplexing

Refer to device-specific data manual for pin multiplexing details.

### 2.5 Memory Map

See your device-specific data manual for information describing the device memory-map.

### 2.6 SDRAM Controller and Interface

The EMIFB can gluelessly interface to most standard SDR SDRAM devices and support such features as self-refresh mode and prioritized refresh. In addition, it provides flexibility through programmable parameters such as the refresh rate, CAS latency, and many SDRAM timing parameters. The following sections include details on how to interface and properly configure the EMIFB to perform read and write operations to externally connected SDR SDRAM devices.

### 2.6.1 SDRAM Commands

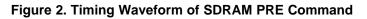

The EMIFB supports the SDRAM commands described in Table 2. Table 3 shows the truth table for the SDRAM commands, and an example timing waveform of the PRE command is shown in Figure 2. EMB\_A[10] is pulled low in this example to deactivate only the bank specified by the EMB\_BA pins.

| Command | Function                                                                                                                                                                                                                                         |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PRE     | <b>Precharge.</b> Depending on the value of EMB_A[10], the PRE command either deactivates the open row in all banks $(EMB_A[10] = 1)$ or only the bank specified by the EMB_BA[1:0] pins $(EMB_A[10] = 0)$ .                                     |

| ACTV    | Activate. The ACTV command activates the selected row in a particular bank for the current access.                                                                                                                                               |

| READ    | <b>Read.</b> The READ command outputs the starting column address and signals the SDRAM to begin the burst read operation. Address EMB_A[10] is always pulled low to avoid auto precharge. This allows for better bank interleaving performance. |

| WRT     | Write. The WRT command outputs the starting column address and signals the SDRAM to begin the burst write operation. Address EMB_A[10] is always pulled low to avoid auto precharge. This allows for better bank interleaving performance.       |

| ВТ      | Burst terminate. The BT command is used to truncate the current read or write burst request.                                                                                                                                                     |

| LMR     | Load mode register. The LMR command sets the mode register of the attached SDRAM devices and is only issued during the SDRAM initialization sequence described in Section 2.6.4.                                                                 |

| REFR    | Auto refresh. The REFR command signals the SDRAM to perform an auto refresh according to its internal address.                                                                                                                                   |

| SLFR    | Self refresh. The self refresh command places the SDRAM into self-refresh mode, during which it provides its own clock signal and auto refresh cycles.                                                                                           |

| NOP     | No operation. The NOP command is issued during all cycles in which one of the above commands is not issued.                                                                                                                                      |

| Table 2. | EMIF | SDRAM | Commands |

|----------|------|-------|----------|

|----------|------|-------|----------|

| SDRAM<br>Pins: | СКЕ       | CS     | RAS     | CAS     | WE     | BA[1:0]     | A[12:11]     | A[10]     | A[9:0]     |

|----------------|-----------|--------|---------|---------|--------|-------------|--------------|-----------|------------|

| EMIFB<br>Pins: | EMB_SDCKE | EMB_CS | EMB_RAS | EMB_CAS | EMB_WE | EMB_BA[1:0] | EMB_A[12:11] | EMB_A[10] | EMB_A[9:0] |

| PRE            | Н         | L      | L       | Н       | L      | Bank/X      | Х            | L/H       | х          |

| ACTV           | н         | L      | L       | н       | н      | Bank        | Row          | Row       | Row        |

| READ           | Н         | L      | н       | L       | н      | Bank        | Column       | L         | Column     |

| WRT            | Н         | L      | н       | L       | L      | Bank        | Column       | L         | Column     |

| BT             | н         | L      | н       | н       | L      | Х           | Х            | х         | х          |

| LMR            | н         | L      | L       | L       | L      | Х           | Mode         | Mode      | Mode       |

| REFR           | Н         | L      | L       | L       | н      | Х           | Х            | х         | х          |

| SLFR           | L         | L      | L       | L       | н      | х           | Х            | х         | х          |

| NOP            | Н         | L      | н       | Н       | н      | х           | Х            | х         | х          |

### Table 3. Truth Table for SDRAM Commands

### 2.6.2 Interfacing to SDRAM

The EMIFB supports a glueless interface to SDRAM devices with the following characteristics:

- Pre-charge bit is A[10]

- The number of column address bits is 8, 9, 10 or 11

- The number of row address bits is 13(in case of mobile SDR, number of row address bits can be 9, 10, 11, 12, or 13)

- The number of internal banks is 1, 2 or 4

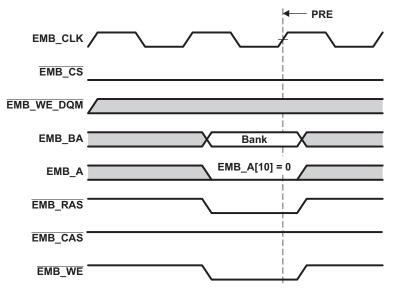

Figure 3 shows an interface between the EMIFB and a  $2M \times 16 \times 4$  bank SDRAM device. In addition, Figure 4 shows an interface between the EMIFB and a  $2M \times 32 \times 4$  bank SDRAM device and Figure 5 shows an interface between the EMIFB and two  $4M \times 16 \times 4$  bank SDRAM devices. Refer to Table 4, as an example that shows additional list of commonly-supported SDRAM devices and the required connections for the address pins. Note that in Table 4, page size/column size (not indicated in the table) is varied to get the required addressability range.

| EMIFB         |          | SDRAM<br>2M x 16 x 4 |

|---------------|----------|----------------------|

| EMB_CS        |          | CE Bank              |

| EMB_CAS       |          | CAS                  |

| EMB_RAS       | •        | RAS                  |

| EMB_WE        | •        | WE                   |

| EMB_CLK       | •        | CLK                  |

| EMB_SDCKE     | •        | CKE                  |

| EMB_BA[1:0]   | ► ►      | BA[1:0]              |

| EMB_A[11:0]   |          | A[11:0]              |

| EMB_WE_DQM[0] |          | LDQM                 |

| EMB_WE_DQM[1] | <b>→</b> | UDQM                 |

| EMB_D[15:0]   | ← →      | DQ[15:0]             |

|               |          |                      |

| Figure 3. | EMIFB to | 2M × 16 > | < 4 bank SD | <b>RAM Interface</b> |

|-----------|----------|-----------|-------------|----------------------|

|-----------|----------|-----------|-------------|----------------------|

Figure 5. EMIFB to Dual  $4M \times 16 \times 4$  bank SDRAM Interface

Table 4. Example of 32-bit EMIFB Address Pin Connections

| SDRAM Size | Width | Banks |       | Address Pins |

|------------|-------|-------|-------|--------------|

| 64M bits   | ×16   | 4     | SDRAM | A[11:0]      |

|            |       |       | EMIFB | EMB_A[11:0]  |

|            | ×32   | 4     | SDRAM | A[10:0]      |

|            |       |       | EMIFB | EMB_A[10:0]  |

| 128M bits  | ×16   | 4     | SDRAM | A[11:0]      |

|            |       |       | EMIFB | EMB_A[11:0]  |

|            | ×32   | 4     | SDRAM | A[11:0]      |

|            |       |       | EMIFB | EMB_A[11:0]  |

| 256M bits  | ×16   | 4     | SDRAM | A[12:0]      |

|            |       |       | EMIFB | EMB_A[12:0]  |

|            | ×32   | 4     | SDRAM | A[11:0]      |

|            |       |       | EMIFB | EMB_A[11:0]  |

| 512M bits  | ×16   | 4     | SDRAM | A[12:0]      |

|            |       |       | EMIFB | EMB_A[12:0]  |

|            | ×32   | 4     | SDRAM | A[12:0]      |

|            |       |       | EMIFB | EMB_A[12:0]  |

| SDRAM Size | Width | Banks |       | Address Pins |

|------------|-------|-------|-------|--------------|

| 64M bits   | ×16   | 4     | SDRAM | A[11:0]      |

|            |       |       | EMIFB | EMB_A[11:0]  |

| 128M bits  | ×16   | 4     | SDRAM | A[11:0]      |

|            |       |       | EMIFB | EMB_A[11:0]  |

### 2.6.3 SDRAM Configuration Registers

The operation of the EMIFB SDRAM interface is controlled by programming the appropriate configuration registers. This section describes the purpose and function of each configuration register, refer to Section 3 for a more detailed description of each register. The following tables list the SDRAM configuration registers, along with a description of each of their programmable fields.

**Note:** Writing to any of the fields in SDCFG and SDCFG2 causes the EMIFB to abandon whatever it is currently doing and trigger the SDRAM initialization procedure described in Section 2.6.4.

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Description                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IBANK_POS Internal bank position. Set to 1 to assign internal bank address bits from logical address a<br>in Table 17(this addressing scheme is normally used in case of mobile SDRAM). Clear to 0<br>internal bank address bits from logical address as shown in Table 15 and Table 16 (these a<br>schemes are normally used in case of SDR SDRAM). This bit is writeable only when the<br>BOOT_UNLOCK bit is unlocked.                                                                                                            |                                                                                                                                                                                                                  |

| MSDRAM_ENABLE mobile SDR enable.Both SDREN and MSDRAM_ENABLE should be set to 1 to enable mot<br>This bit is writeable only when the BOOT_UNLOCK bit is unlocked.                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                  |

| BOOT_UNLOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Boot Unlock.Set to 1 to change the values of the fields that are affected by the BOOT_UNLOCK bit.                                                                                                                |

| SDREN SDR Enable. This bit enables EMIFB to interface to SDRAM type memories. This bit is set to 1 default.                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                  |

| TIMUNLOCK Timing Unlock.Controls the write permission settings for the SDRAM timing 1 register (SDTIM SDRAM timing 2 register (SDTIM2)                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                  |

| NM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>Narrow Mode.</b> This bit defines the width of the data bus between the EMIF and the attached SDRAM device. When set to 1, the data bus is set to 16-bits; when cleared to 0, the data bus is set to 32-bits. |

| CL CAS latency. This field defines the number of clock cycles between when an SDRAM issues command and when the first piece of data appears on the bus. The value in this field is sent attached SDRAM device via the LOAD MODE REGISTER command during the SDRAM initi procedure as described in Section 2.6.4. Only values of 2h (CAS latency = 2) and 3h (CAS latency = 3) are supported and are written to this field. A 1 must be simultaneously written to the TIMU bit field of SDCFG in order to write to the CL bit field. |                                                                                                                                                                                                                  |

| EBANK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Number of External SDRAM Banks (or chip selects). This field defines the number of chip selects are utilized on the SDRAM interface:                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ul> <li>When EBANK = 0, CS[0] is used (single external bank). Always write 0 to this field.</li> </ul>                                                                                                          |

| IBANK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Number of Internal SDRAM Banks. This field defines the number of banks inside the attached SDRAM devices in the following way:                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ul> <li>When IBANK = 0, 1 internal bank is used</li> </ul>                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ul> <li>When IBANK = 1h, 2 internal banks are used</li> </ul>                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ul> <li>When IBANK = 2h, 4 internal banks are used</li> <li>This field value affects the mapping of logical addresses to SDRAM row, column, and bank addresses. See Section 2.6.12 for details.</li> </ul>      |

| Table 6. Description of the SDRAM Configuration Register (SDCFG) |

|------------------------------------------------------------------|

|------------------------------------------------------------------|

| Parameter | Description                                                                                                                                                                                                                                     |  |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PAGESIZE  | Page Size. This field defines the internal page size of the attached SDRAM devices in the following way:                                                                                                                                        |  |  |

|           | <ul> <li>When PAGESIZE = 0, 256-word pages are used, requiring 8 column address bits.</li> </ul>                                                                                                                                                |  |  |

|           | <ul> <li>When PAGESIZE = 1h, 512-word pages are used, requiring 9 column address bits.</li> </ul>                                                                                                                                               |  |  |

|           | <ul> <li>When PAGESIZE = 2h, 1024-word pages are used, requiring 10 column address bits.</li> </ul>                                                                                                                                             |  |  |

|           | <ul> <li>When PAGESIZE = 3h, 2048-word pages are used, requiring 11 column address bits.<br/>This field value affects the mapping of logical addresses to SDRAM row, column, and bank<br/>addresses. See Section 2.6.12 for details.</li> </ul> |  |  |

### Table 6. Description of the SDRAM Configuration Register (SDCFG) (continued)

### Table 7. Description of the SDRAM Refresh Control Register (SDRFC)

| Parameter                                                                                                                         | Description<br>Low Power Mode. This bit enables the self-refresh mode of the attached SDRAM devices (which is<br>the lowest power mode).                                                                      |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LP_MODE                                                                                                                           |                                                                                                                                                                                                               |  |  |

| MCLKSTOP_EN mclk stop enable. mclk can stopped only if this bit is set.                                                           |                                                                                                                                                                                                               |  |  |

| SR_PD Self Refresh/ Power Down select. This bit along with LP_MODE determines if SDRAM is placed in self-refresh/power-down mode. |                                                                                                                                                                                                               |  |  |

| REFRESH_RATE                                                                                                                      | <b>Refresh Rate</b> . This field controls the rate at which attached SDRAM devices will be refreshed. The following equation can be used to determine the required value of REFRESH_RATE for an SDRAM device: |  |  |

|                                                                                                                                   | <ul> <li>REFRESH_RATE = (EMIFB clock rate)/(Required SDRAM Refresh Rate)</li> <li>More information about the operation of the SDRAM refresh controller can be found in Section 2.6.6.</li> </ul>              |  |  |

### Table 8. Description of the SDRAM Timing 1 Register (SDTIM1)

| Parameter | Description                                                                                                                                                                                        |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T_RFC     | SDRAM Timing Parameters. These fields configure the EMIFB to comply with the AC timing                                                                                                             |

| T_RP      | requirements of the attached SDRAM devices. This allows the EMIFB to avoid violating SDRAM<br>timing constraints and to more efficiently schedule its operations. More details about each of these |

| T_RCD     | parameters can be found in the register description in Section 3.4. These parameters are set to                                                                                                    |

| T_WR      | satisfy the corresponding timing requirements found in the SDRAM's datasheet.                                                                                                                      |

| T_RAS     |                                                                                                                                                                                                    |

| T_RC      |                                                                                                                                                                                                    |

| T_RRD     |                                                                                                                                                                                                    |

### Table 9. Description of the SDRAM Timing 2 Register (SDTIM2)

| Parameter | Description<br>Maximum number of refresh_rate intervals from Activate to Precharge command.                                                                                                                                                                                                                                                                                                                                                              |  |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| T_RAS_MAX |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| T_XS      | Self Refresh Exit Parameter. The T_XS field of this register informs the EMIFB about the minimum number of EMB_CLK cycles required between exiting Self Refresh and issuing any command. This parameter is set to satisfy the t <sub>XSR</sub> value for the attached SDRAM device.           The T_CKE field fixes the minimum time between CKE transitions. This parameter is set to satisfy the t <sub>RAS</sub> value for the attached SDRAM device. |  |  |

| T_CKE     |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

### Table 10. Description of the SDRAM Configuration 2 Register (SDCFG2)

| Parameter | Description                                                                                                                                                                                                               |  |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PASR      | Partial Array Self Refresh. These bits get loaded into the Extended Mode Register of a mobile SDRAM during initialization. A write to this field will cause the EMIFB to start the SDRAM initialization sequence.         |  |  |

| ROWSIZE   | <b>Row Size.</b> Defines the number of row address bits of connected SDRAM devices. This bit is used only in case of mobile SDRAM. A write to this field will cause the EMIFB to start the SDRAM initialization sequence. |  |  |

### 2.6.4 SDRAM/mobile SDRAM Auto-Initialization Sequence

The EMIFB automatically performs an SDRAM initialization sequence, regardless of whether it is interfaced to an SDRAM device, when the following event occurs:

- A write is performed to any of the two least significant bytes of the SDRAM configuration register (SDCFG)

- In case of mobile SDR, initialization sequence also starts when a write is performed to SDRAM configuration 2 register (SDCFG2)

An SDRAM/mobile SDR initialization sequence consists of the following steps:

- First, software must set the SDREN bit (in case of mobile SDRAM, both SDREN and MSDRAM\_ENABLE should be set to 1) in the SDRAM configuration register (SDCFG) (assuming clocking and pin multiplexing are already configured accordingly).

- If the initialization sequence is activated by a write to SDCFG, and if any of the SDRAM banks are open, the EMIFB issues a PRE command with EMB\_A[10] held high to indicate all banks. This is done so that the maximum ACTV to PRE timing for an SDRAM is not violated.

- 3. The EMIFB drives EMB\_SDCKE high and begins continuously issuing NOP commands until eight SDRAM refresh intervals have elapsed. An SDRAM refresh interval is equal to the value of the REFRESH\_RATE field of the SDRAM refresh control register (SDRFC), divided by the frequency of EMB\_CLK (REFRESH\_RATE/f<sub>CLK</sub>). This step is used to avoid violating the Power-up constraint of most SDRAM devices that requires 200 μs (sometimes 100 μs) between receiving stable Vdd and CLK and the issuing of a PRE command. Depending on the frequency of EMB\_CLK, this step may or may not be sufficient to avoid violating the SDRAM constraint. See Section 2.6.5 for more information.

- 4. After the refresh intervals have elapsed, the EMIFB issues a PRE command with EMB\_A[10] held high to indicate all banks.

- 5. The EMIFB issues eight AUTO REFRESH commands.

- 6. If initialization sequence is of mobile SDRAM, EMIFB issues LMR command with EMB\_A[6:0] pins set as described in Table 11.

- 7. Then, EMIFB issues the LMR command with the EMB\_A[9:0] pins set as described in Table 12. This step is executed for both SDRAM/mobile SDRAM.

- 8. Finally, the EMIFB performs an auto refresh cycle, which consists of the following steps:

- a. Issuing a PRE command with EMB\_A[10] held high if any banks are open

- b. Issuing a REF command

- c. Interface is idle (awaiting access)

| A[6:5]                                              | A[4:3]                                               | A[2:0]                                                                                         |

|-----------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 0 (SDRAM drive strength; 0= full<br>drive strength) | 0 (Internal Temperature<br>Compensated Self Refresh) | These bits are set according to the PASR field in the SDRAM configuration 2 register (SDCFG2). |

#### Table 11. mobile SDRAM LOAD MODE REGISTER Command

### Table 12. SDRAM/mobile SDRAM LOAD MODE REGISTER Command

| A[9:7]                                                                     | A[6:4]                                                                                                                                    | A[3]                                                                     | A[2:0]                                                                                                                                         |

|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 (Write bursts are<br>of the programmed<br>burst length in<br>EMB_A[2:0]) | These bits control the CAS latency of the SDRAM and are set according to CL field in the SDRAM configuration register (SDCFG) as follows: | 0 (Sequential Burst<br>Type. Interleaved<br>Burst Type not<br>supported) | These bits control the burst length of the SDRAM and are set according to the NM field in the SDRAM configuration register (SDCFG) as follows: |

|                                                                            | <ul> <li>If CL = 2h, EMB_A[6:4] = 2h<br/>(CAS latency = 2)</li> </ul>                                                                     |                                                                          | <ul> <li>If NM = 0, EMB_A[2:0] = 2h<br/>(Burst Length = 4)</li> </ul>                                                                          |

|                                                                            | <ul> <li>If CL = 3h, EMB_A[6:4] = 3h<br/>(CAS latency = 3)</li> </ul>                                                                     |                                                                          | <ul> <li>If NM = 1, EMB_A[2:0] = 3h<br/>(Burst Length = 8)</li> </ul>                                                                          |

### 2.6.5 SDRAM Configuration Procedure

After initial power-on, follow the procedure listed below before performing any EMIFB memory requests. Note that the SDRAM power-up constraint specifies that 200  $\mu$ s must exist between receiving stable Vdd and CLK and the issuing of a PRE command. Initialization software and system design must ensure that this constraint is met before executing the initialization procedure.

- 1. Place the SDRAM into Self-Refresh Mode by setting the LP\_MODE bit and SR\_PD bit of the SDRAM refresh control register (SDRFC) to 1 and 0, respectively. Place the SDRAM into Self-Refresh mode when changing the frequency of EMB\_CLK to avoid incurring the 200 μs power-up constraint again.

- Program the PLL controller and configure the EMIFB clock mux selection (in the System Configuration Module) to attain the desired EMB\_CLK clock frequency. Refer to the device data manual for details on programming the PLL controller. The frequency of the memory clock must meet the timing requirements in the SDRAM manufacturer's documentation and the timing limitations shown in the electrical specifications of the device data manual.

- Enable SDR mode of the EMIFB by writing 1 to the SDREN bit (write 1 to both SDREN and MSDRAM\_ENABLE to enable mobile SDR) in the SDRAM configuration register (SDCFG). Also ensure that pin multiplexing is properly configured.

- 4. Program SDTIM1 and SDTIM2 to satisfy the timing requirements for the attached SDRAM device. Take the timing parameters from the SDRAM datasheet.

- 5. Program the REFRESH\_RATE field of SDRFC to match that of the attached device's refresh interval. See Section 2.6.6.1 for details on determining the appropriate value.

- 6. Program SDCFG to match the characteristics of the attached SDRAM device. This will cause the auto-initialization sequence in Section 2.6.4 to be re-run. This second initialization generally takes much less time due to the increased frequency of EMB\_CLK.

After following the above procedure, the EMIFB is ready to perform accesses to the attached SDRAM device. If a frequency change is desired after this configuration has been executed, first put the SDRAM into Self-Refresh mode using a byte-write to the upper byte of SDCFG to avoid restarting the SDRAM auto-initialization sequence. Then release the SDRAM from self-refresh mode and repeat steps 4 through 6 of the above procedure.

### 2.6.6 EMIFB Refresh Controller

An SDRAM device requires that each of its rows be refreshed at a minimum required rate. The EMIFB can meet this constraint by performing auto refresh cycles at or above this required rate. An auto refresh cycle consists of issuing a PRE command to all banks of the SDRAM device followed by issuing a REFR command. To inform the EMIFB of the required rate for performing auto refresh cycles, the REFRESH\_RATE field of the SDRAM refresh control register (SDRFC) must be programmed. The EMIF will use this value along with two internal counters to automatically perform auto refresh cycles at the required rate. The auto refresh cycles cannot be disabled, even if the EMIFB is not interfaced with an SDRAM. The remainder of this section details the EMIFB's refresh scheme and provides an example for determining the appropriate value to place in the REFRESH\_RATE field of SDRFC.

The two counters used to perform auto-refresh cycles are a 13-bit refresh interval counter and a 4-bit refresh backlog counter. After SDREN = 1 and upon writing to the REFRESH\_RATE field, the refresh interval counter is loaded with the value from REFRESH\_RATE field and begins decrementing, by one, each EMIFB clock cycle. When the refresh interval counter reaches zero, the following actions occur:

- The refresh interval counter is reloaded with the value from the REFRESH\_RATE field and restarts decrementing.

- The 4-bit refresh backlog counter increments unless it has already reached its maximum value.

Architecture

www.ti.com

The refresh backlog counter records the number of auto refresh cycles that the EMIFB currently has outstanding. This counter is decremented by one each time an auto refresh cycle is performed and incremented by one each time the refresh interval counter expires. The refresh backlog counter saturates at the values of 0000b and 1111b. The EMIFB uses the refresh backlog counter to determine the urgency with which an auto refresh cycle is to be performed. The four levels of urgency are described in Table 13. This refresh scheme allows the required refreshes to be performed with minimal impact on access requests.

| Urgency Level   | Refresh Backlog<br>Counter Range | Action Taken                                                                                                                                                                                                              |

|-----------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Refresh May     | 1-3                              | An auto-refresh cycle is performed only if the EMIFB has no requests pending and none of the SDRAM banks are open.                                                                                                        |

| Refresh Release | 4-7                              | An auto-refresh cycle is performed if the EMIFB has no requests pending, regardless of whether any SDRAM banks are open.                                                                                                  |

| Refresh Need    | 8-11                             | An auto-refresh cycle is performed at the completion of the current access unless there are read requests pending.                                                                                                        |

| Refresh Must    | 12-15                            | Multiple auto-refresh cycles are performed at the completion of the current access<br>until the Refresh Release urgency level is reached. At that point, the EMIFB can begin<br>servicing any new read or write requests. |

### Table 13. Refresh Urgency Levels

### 2.6.6.1 Determining the Appropriate Value for the REFRESH\_RATE Field

The value programmed into the REFRESH\_RATE field of SDRFC can be calculated by using the frequency of the EMB\_CLK signal ( $f_{CLK}$ ) and the required refresh rate of the SDRAM ( $f_{Refresh}$ ). The following formula can be used:

### $REFRESH_RATE \leq f_{CLK} / f_{Refresh}$

The SDRAM datasheet often communicates the required SDRAM Refresh Rate in terms of the number of REFR commands required in a given time interval. The required SDRAM Refresh Rate in the formula above can be therefore be calculated by dividing the number of required cycles per time interval ( $n_{cycles}$ ) by the time interval given in the datasheet ( $t_{Refresh Period}$ ):

### $f_{\text{Refresh}} = n_{\text{cycles}} / t_{\text{Refresh Period}}$

Combining these formulas, the value programmed into the REFRESH\_RATE field can be computed as:

$REFRESH\_RATE \leq f_{CLK} \times t_{Refresh \ Period} \ / \ n_{cycles}$

The following example illustrates calculating the value of REFRESH\_RATE. Given that:

- f<sub>CLK</sub> = 133 MHZ (frequency of the EMIFB clock)

- t<sub>Refresh Period</sub> = 64 ms (required refresh interval of the SDRAM)

- n<sub>cycles</sub> = 8192 (number of cycles in a refresh interval for the SDRAM)

REFRESH\_RATE can be calculated as:

REFRESH\_RATE = 133 MHZ × 64 ms/8192

REFRESH\_RATE = 1039.06

REFRESH\_RATE = 1039 cycles = 40Fh cycles

### 2.6.7 Self-Refresh Mode

The EMIFB can be programmed to enter the self-refresh state by setting the LP\_MODE bit and SR\_PD bit of the SDRAM refresh control register (SDRFC) to 1 and 0, respectively. This will cause the EMIFB to issue the SLFR command after completing any outstanding SDRAM access requests and clearing the refresh backlog counter by performing one or more auto refresh cycles. This places the attached SDRAM device into self-refresh mode in which it consumes a minimal amount of power while performing its own refresh cycles.

While in the self-refresh state, the EMIFB continues to service register accesses as normal.

The EMIFB will exit from the self-refresh state, if any of the following events occur:

- The LP\_MODE bit of SDRFC is cleared to 0

- The SR\_PD bit is set to 1

- An SDRAM accesses is requested

The EMIFB exits from the self-refresh state by driving EMB\_SDCKE high and performing an auto refresh cycle.

The attached SDRAM device must be placed into self-refresh mode when changing the frequency of EMB\_CLK using the PLL Controller. If the frequency of EMB\_CLK changes while the SDRAM is not in self-refresh mode, the memory must be reinitialized.

During Self- refresh, if memory/register access request is made, EMIFB comes out of self-refresh state (driving EMB\_SDCKE high) and executes the requests; after which it again goes back to self-refresh state (driving EMB\_SDCKE low).

To use Partial Array Self Refresh for mobile SDR, PASR bits in the SDRAM configuration 2 register must be appropriately programmed. The EMIFB performs bank interleaving. Since the SDRAM is partially refreshed during Partial Array Self Refresh, it is the responsibility of software to move critical data into the banks that are going to be refreshed during Partial Array Self Refresh.

### 2.6.8 Power-Down Mode

To support low-power modes, the EMIFB can be requested to issue a POWERDOWN command to the SDRAM by setting both the LP\_MODE and SR\_PD bits in the SDRAM refresh control register (SDRFC) to 1. When this bit is set, the EMIFB will continue normal operation until all outstanding memory access requests have been serviced and the SDRAM refresh backlog (if there is one) has been cleared. At this point the EMIFB will enter the power-down state. Upon entering this state the EMIF will issue a POWERDOWN command (same as a NOP command but driving EMB\_SDCKE low on the same cycle). The EMIFB then maintains EMB\_SDCKE low until it exits the power-down state.

During the power-down state, the EMIFB services synchronous memory and register accesses as normal.

The EMIFB will exit from the power-down state, if any of the following events occur:

- The LP\_MODE bit of SDRFC is cleared to 0

- The SR\_PD bit is cleared to 0

- An SDRAM accesses is requested

- Refresh (REFR) command is to be sent to SDRAM.

During power-down, if memory/register access request is made, EMIFB comes out of the power-down state (driving EMB\_SDCKE high) and executes the requests; after which it again goes back to the power-down state (driving EMB\_SDCKE low).

### 2.6.9 Partial Array Self Refresh for mobile SDRAM

This is applicable only to mobile SDRAM, when using the addressing scheme as described in Table 17. For additional power savings during self-refresh, the partial array self-refresh (PASR) feature of mobile SDR allows to select the amount of memory that will be refreshed during self-refresh. Use the partial array self-refresh (PASR) bit field in the SDRAM configuration 2 register (SDCFG2) to select the amount of memory to refresh during self-refresh. As shown in Table 14 you may select either 4, 2, 1, 1/2, or 1/4 bank(s). The PASR bits are loaded into the extended mode register of the mobile SDR device, during autoinitialization (see Section 2.6.4). The EMIFB performs bank interleaving when the internal bank position (IBANKPOS) bit in SDRAM configuration register (SDCFG) is cleared to 0. Since the SDRAM banks are only partially refreshed during partial array self-refresh, it is recommended that you set IBANKPOS to 1 to avoid bank interleaving. Refer to Section 2.6.12 for more information on IBANKPOS and addressing mapping in general.

| Bit Field | Bit Value | Bit Description              |  |

|-----------|-----------|------------------------------|--|

| PASR      | 0         | Refresh banks 0, 1, 2, and 3 |  |

|           | 1h        | Refresh banks 0 and 1        |  |

|           | 2h        | Refresh bank 0               |  |

|           | 3h        | Reserved                     |  |

|           | 4h        | Reserved                     |  |

|           | 5h        | Refresh 1/2 of bank 0        |  |

|           | 6h        | Refresh 1/4 of bank 0        |  |

|           | 7h        | Reserved                     |  |

## Table 14. PASR Bitfield in SDRAM Configuration 2 Register (SDCFG2) Configuration

### 2.6.10 SDRAM Read Operation

When the EMIFB receives a read request to SDRAM, it performs one or more read access cycles. A read access cycle begins with the issuing of the ACTV command to select the desired bank and row of the SDRAM device. After the row has been opened, the EMIFB proceeds to issue a READ command while specifying the desired bank and column address. EMB\_A[10] is held low during the READ command to avoid auto-precharging. The READ command signals the SDRAM device to start bursting data from the specified address while the EMIFB issues NOP commands. Following a READ command, the CL field of the SDRAM configuration register (SDCFG) defines how many delay cycles will be present before the read data appears on the data bus. This is referred to as the CAS latency.

Figure 6 shows the signal waveforms for a basic SDRAM read operation in which a burst of data is read from a single page. When the EMIFB SDRAM interface is configured to 32-bit by clearing the NM bit of the SDRAM configuration register (SDCFG) to 0, a burst size of four is used. When configured to 16-bit by setting NM to 1, a burst size of eight is used. Figure 6 shows a burst size of four.

Figure 6. Timing Waveform for Basic SDRAM Read Operation

The EMIFB will truncate a series of bursting data if the remaining addresses of the burst are not required to complete the request. The EMIFB can truncate the burst in three ways:

- By issuing another READ to the same page in the same bank.

- By issuing a PRE command in order to prepare for accessing a different page of the same bank.

- By issuing a BT command in order to prepare for accessing a page in a different bank.

Several other pins are also active during a read access. The EMB\_WE\_DQM[3:0] pins are driven low during the READ commands and are kept low during the NOP commands that correspond to the burst request. The state of the other EMIFB pins during each command can be found in Table 3.

The EMIFB schedules its commands based on the timing information that is provided to it in the SDRAM timing registers (SDTIM1 and SDTIM2). The values for the timing parameters in this register are chosen to satisfy the timing requirements listed in the SDRAM datasheet. The EMIFB uses this timing information to avoid violating any timing constraints related to issuing commands. This is commonly accomplished by inserting NOP commands between various commands during an access. Refer to the register description of SDTIM1 and SDTIM2 for more details on the various timing parameters.

Architecture

### 2.6.11 SDRAM Write Operations

When the EMIFB receives a write request to SDRAM, it performs one or more write-access cycles. A write-access cycle begins with the issuing of the ACTV command to select the desired bank and row of the SDRAM device. After the row has been opened, the EMIFB proceeds to issue a WRT command while specifying the desired bank and column address. EMB\_A[10] is held low during the WRT command to avoid auto-precharging. The WRT command signals the SDRAM device to start writing a burst of data to the specified address while the EMIFB issues NOP commands. The associated write data will be placed on the data bus in the cycle concurrent with the WRT command and with subsequent burst continuation NOP commands.

Figure 7 shows the signal waveforms for a basic SDRAM write operation in which a burst of data is read from a single page. When the EMIFB SDRAM interface is configured to 32-bit by clearing the NM bit of the SDRAM configuration register (SDCFG) to 0, a burst size of four is used. When configured to 16-bit by setting NM to 1, a burst size of eight is used. Figure 7 shows a burst size of four.

Figure 7. Timing Waveform for Basic SDRAM Write Operation

The EMIFB will truncate a series of bursting data if the remaining addresses of the burst are not part of the write request. The EMIFB can truncate the burst in three ways:

- By issuing another WRT to the same page

- By issuing a PRE command in order to prepare for accessing a different page of the same bank

- By issuing a BT command in order to prepare for accessing a page in a different bank

Several other pins are also active during a write access. The EMB\_WE\_DQM[3:0] pins are driven to select which bytes of the data word will be written to the SDRAM device. They are also used to mask out entire undesired data words during a burst access. The state of the other EMIFB pins during each command can be found in Table 3.

EMIFB schedules its commands based on the timing information that is provided to it in the SDRAM timing registers (SDTIM1 and SDTIM2). The values for the timing parameters in this register are chosen to satisfy the timing requirements listed in the SDRAM datasheet. EMIFB uses this timing information to avoid violating any timing constraints related to issuing commands. This is commonly accomplished by inserting NOP commands during various cycles of an access. Refer to the register description of SDTIM1 and SDTIM2 for more details on the various timing parameters.

### 2.6.12 Mapping from Logical Address to EMIFB Pins

When the EMIFB receives an SDRAM access request, it must convert the address of the access into the appropriate signals to send to the SDRAM device. The details of an example address mapping are shown in Table 15 for 32-bit operation and in Table 16 for 16-bit operation. (In both the examples, a 13-bit row address is used to calculate the maximum reach. See your device-specific data manual to know the possible values of IBANK and PAGESIZE for EMIFB). Using the settings of the IBANK and PAGESIZE fields of the SDRAM configuration register (SDCFG), the EMIFB determines which bits of the logical address will be mapped to the SDRAM row, column, and bank addresses.

As the logical address is incremented by one word (32-bit operation) or one halfword (16-bit operation), the column address is likewise incremented by one until a page boundary is reached. When the logical address increments across a page boundary, the EMIFB moves into the same page in the next bank of the attached device by incrementing the bank address EMB\_BA and resetting the column address. The page in the previous bank is left open until it is necessary to close it. This method of traversal through the SDRAM banks helps maximize the number of open banks inside of the SDRAM and results in an efficient use of the device. There is no limitation on the number of banks than can be open at one time, but only one page within a bank can be open at a time. To use such an addressing scheme, clear the internal bank position (IBANK\_POS) bit in SDCFG to 0. This addressing scheme is used when EMIFB memory controller is configured to interface with SDRAM.

The EMIFB uses the <u>EMB\_WE\_DQM</u> pins during a WRT command to mask out selected bytes or entire words. The <u>EMB\_WE\_DQM</u> pins are always low during a READ command.

When using mobile SDRAM, set IBANK\_POS = 1, and this uses an addressing scheme as described in Table 17. See device data manual to know possible values of ROWSIZE, IBANK, and PAGESIZE for EMIFB configured to interface with mobile SDRAM device.